Một thanh ghi dịch chuyển vạn năng (Universal Shift Register – USR) là một loại thanh ghi có khả năng dịch chuyển dữ liệu sang phải, sang trái và nạp song song. USR được sử dụng như các phần tử bộ nhớ trong máy tính. Bài viết này sẽ phân tích và mô phỏng hoạt động của một thanh ghi dịch chuyển vạn năng 4 bit được viết bằng Verilog, kèm theo testbench để kiểm chứng hoạt động.

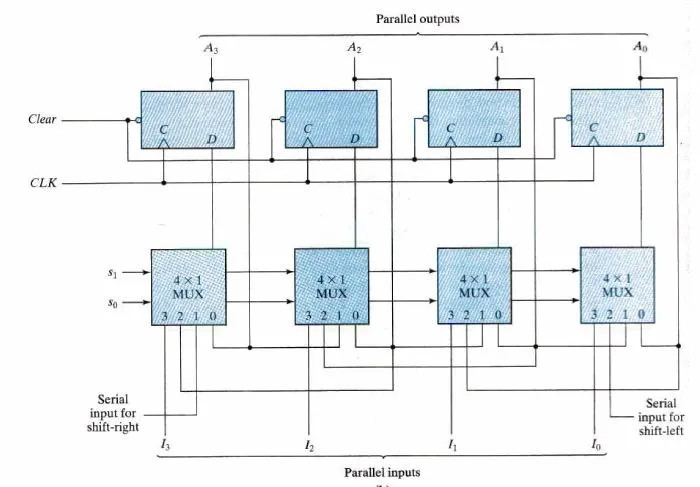

Thanh ghi dịch chuyển 4 bit này có thể nhận dữ liệu và tín hiệu điều khiển từ người dùng và thực hiện các thao tác dữ liệu theo chế độ hoạt động được chỉ định. Thiết kế của USR 4 bit bao gồm 4 flip-flop và 4 bộ ghép kênh 4×1. Tất cả 4 bộ ghép kênh chia sẻ cùng các đường chọn (S1 và S0) để lựa chọn chế độ hoạt động cho thanh ghi dịch. Các đầu vào của đường chọn sẽ chọn đầu vào phù hợp cho các flip-flop.

Mô hình mạch này có các kết nối sau: đầu vào thứ nhất được kết nối với chân đầu ra của flip-flop tương ứng; đầu vào thứ hai được kết nối với đầu ra của flip-flop liền trước để thực hiện dịch phải; đầu vào thứ ba được kết nối với đầu ra của flip-flop liền sau để thực hiện dịch trái; đầu vào thứ tư được kết nối với các bit riêng lẻ của dữ liệu đầu vào để nạp song song.

Hoạt động của USR phụ thuộc vào các đầu vào của đường chọn. Cụ thể, với đầu vào ’00’, thanh ghi ở trạng thái khóa, giữ nguyên dữ liệu. Đầu vào ’01’ thực hiện dịch phải, ’10’ thực hiện dịch trái và ’11’ cho phép nạp song song dữ liệu vào thanh ghi.

USR có nhiều ưu điểm như: thực hiện được 3 thao tác dịch trái, dịch phải và nạp song song; lưu trữ dữ liệu tạm thời; thực hiện chuyển đổi dữ liệu nối tiếp sang nối tiếp, nối tiếp sang song song, song song sang nối tiếp và song song sang song song; hoạt động như một giao diện giữa các thiết bị trong quá trình truyền dữ liệu.

Ứng dụng của USR rất đa dạng, bao gồm: mở rộng I/O trong vi điều khiển; chuyển đổi dữ liệu nối tiếp sang nối tiếp, song song sang song song, nối tiếp sang song song; truyền dữ liệu song song và nối tiếp; làm phần tử bộ nhớ trong máy tính; ứng dụng trong trì hoãn thời gian và thao tác dữ liệu; sử dụng trong bộ đếm tần số, bộ đếm nhị phân và đồng hồ kỹ thuật số.

Để mô phỏng và tổng hợp USR, ta sử dụng các công cụ như Icarus Verilog (mô phỏng), GTKWave (hiển thị dạng sóng), Yosys (tổng hợp) và OpenLane (thiết kế ASIC).

Kết quả mô phỏng trước khi tổng hợp với dữ liệu đầu vào ‘1001’ cho thấy các hoạt động nạp song song, dịch phải, dịch trái và trạng thái khóa hoạt động chính xác. Sau khi tổng hợp, ta có thể chạy GLS (Gate Level Simulation) để kiểm tra lại hoạt động logic của mạch ở mức cổng.

OpenLane được sử dụng để thực hiện các bước thiết kế vật lý, bao gồm floorplan, placement, clock tree synthesis và routing. Sau khi hoàn thành routing, ta có thể kiểm tra diện tích và công suất tiêu thụ của mạch. Cuối cùng, phân tích thời gian tĩnh (STA) được thực hiện để đảm bảo mạch hoạt động đúng với tần số yêu cầu.