Thanh ghi CPSR (Current Program Status Register) là một thanh ghi 32-bit quan trọng trong kiến trúc ARM, chứa thông tin về trạng thái hiện tại của bộ xử lý. Nó ảnh hưởng đến hoạt động của CPU và quyết định cách thức thực thi các lệnh.

CPSR lưu trữ các cờ điều kiện (condition flags), chế độ bộ xử lý (processor mode), và thông tin điều khiển khác. Các cờ điều kiện, bao gồm Negative (N), Zero (Z), Carry (C), và Overflow (V), được cập nhật sau mỗi lệnh toán học hoặc logic, phản ánh kết quả của phép toán. Ví dụ, cờ N được đặt nếu kết quả là âm, cờ Z được đặt nếu kết quả bằng không.

Hình 1: Mô tả trạng thái ban đầu của bộ đệm vòng, với con trỏ đầu và đuôi trùng nhau, cho biết bộ đệm đang trống.

Chế độ bộ xử lý xác định quyền truy cập của chương trình vào các tài nguyên hệ thống. ARM có nhiều chế độ hoạt động khác nhau, bao gồm User, System, Supervisor, Abort, Interrupt, Undefined, và FIQ. Mỗi chế độ có mức độ ưu tiên và quyền hạn riêng. Arm Cpsr Register cho phép hệ điều hành kiểm soát việc chuyển đổi giữa các chế độ này để xử lý các sự kiện khác nhau, như ngắt hoặc lỗi.

Hình 2: Trạng thái của bộ đệm vòng sau khi ký tự đầu tiên được đọc và con trỏ đuôi được tăng lên.

Việc hiểu rõ cấu trúc và chức năng của arm cpsr register là rất quan trọng cho việc lập trình và gỡ lỗi trên hệ thống ARM. Nó cho phép lập trình viên kiểm soát luồng thực thi chương trình, xử lý ngoại lệ, và tối ưu hóa hiệu năng. Ví dụ, bằng cách kiểm tra các cờ điều kiện trong arm cpsr register, lập trình viên có thể quyết định thực hiện các đoạn mã khác nhau dựa trên kết quả của phép toán trước đó.

Hình 3: Bộ đệm vòng trong trạng thái đầy, với một ký tự trống để phân biệt với trạng thái trống.

Thông qua các bit cụ thể trong arm cpsr register, có thể bật hoặc tắt các tính năng như ngắt, chế độ Thumb, và xử lý dấu chấm động. Việc thao tác với arm cpsr register thường được thực hiện thông qua các lệnh đặc biệt của ARM assembly. Tuy nhiên, một số ngôn ngữ lập trình cấp cao cũng cung cấp các hàm hoặc thư viện cho phép truy cập và sửa đổi một số bit trong arm cpsr register.

Hình 4: Con trỏ đầu của bộ đệm vòng vượt qua cuối bộ đệm và quay vòng về đầu.

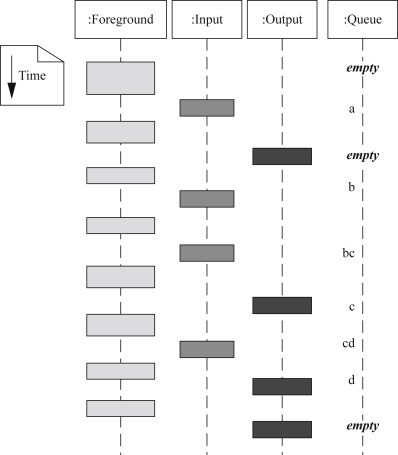

Hình 5: Sơ đồ trình tự UML minh họa hoạt động đan xen giữa chương trình chính, xử lý ngắt đầu vào và đầu ra.

Hình 5: Sơ đồ trình tự UML minh họa hoạt động đan xen giữa chương trình chính, xử lý ngắt đầu vào và đầu ra.