Thanh ghi dịch chuyển vào song song ra nối tiếp (PISO) là một loại thanh ghi dịch chuyển dữ liệu được sử dụng rộng rãi trong kỹ thuật số. Bài viết này sẽ đi sâu vào nguyên lý hoạt động, bảng chân lý, sơ đồ mạch, ứng dụng và code Verilog của thanh ghi PISO, đặc biệt tập trung vào bảng chân lý thanh ghi dịch chuyển vào song song ra nối tiếp (Parallel In Serial Out Shift Register Truth Table).

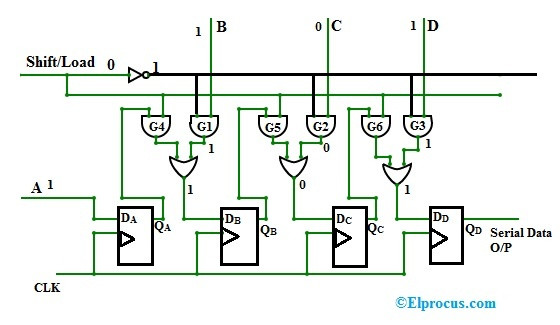

Hình 1: Sơ đồ mạch thanh ghi PISO

Thanh Ghi Dịch Chuyển Vào Song Song Ra Nối Tiếp (PISO) là gì?

Thanh ghi PISO cho phép nhập dữ liệu vào song song, nghĩa là tất cả các bit dữ liệu được nhập cùng một lúc, và xuất dữ liệu ra nối tiếp, nghĩa là từng bit một theo thứ tự. Điều này ngược lại với hoạt động của thanh ghi SIPO (Serial In Parallel Out). Mỗi bit dữ liệu được lưu trữ trong một flip-flop riêng biệt. Dữ liệu được dịch chuyển qua các flip-flop này bằng tín hiệu xung clock.

Nguyên Lý Hoạt Động của Thanh Ghi PISO

Trong thanh ghi PISO, dữ liệu được nạp song song vào các flip-flop thông qua các đường dữ liệu riêng biệt. Sau khi dữ liệu được nạp, mỗi xung clock sẽ dịch chuyển toàn bộ dữ liệu sang phải một vị trí. Bit ở vị trí ngoài cùng bên phải sẽ được xuất ra, trong khi bit ở vị trí ngoài cùng bên trái sẽ nhận giá trị mới (thường là 0). Quá trình này lặp lại cho đến khi tất cả các bit dữ liệu được xuất ra.

Bảng Chân Lý Thanh Ghi Dịch Chuyển Vào Song Song Ra Nối Tiếp

Bảng chân lý mô tả trạng thái đầu ra (QD) dựa trên trạng thái đầu vào và xung clock. Ví dụ với thanh ghi 4-bit:

Bảng 1: Bảng chân lý thanh ghi PISO sau khi nạp dữ liệu 1101

| Xung Clock | QA | QB | QC | QD (Đầu ra) |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 2 | 0 | 1 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 0 | 0 | 1 |

Giải thích:

- Tại xung clock 0, chưa có dữ liệu được nạp, đầu ra là 0.

- Tại xung clock 1, dữ liệu 1101 được nạp, QD xuất ra bit cuối cùng là 1.

- Tại mỗi xung clock tiếp theo, dữ liệu dịch chuyển sang phải một bit và bit cuối cùng được xuất ra tại QD.

Sơ Đồ Mạch và Biểu Đồ Thời Gian

Hình 1 minh họa sơ đồ mạch của một thanh ghi PISO 4 bit sử dụng flip-flop D. Biểu đồ thời gian (timing diagram) sẽ thể hiện sự thay đổi trạng thái của các đầu ra (QA, QB, QC, QD) theo thời gian và xung clock.

Hình 2: Biểu đồ thời gian thanh ghi PISO

Ứng Dụng của Thanh Ghi PISO

Thanh ghi PISO được ứng dụng trong nhiều hệ thống kỹ thuật số, bao gồm:

- Chuyển đổi dữ liệu từ dạng song song sang dạng nối tiếp.

- Tạo độ trễ thời gian trong mạch kỹ thuật số.

- Đọc dữ liệu từ nhiều nút nhấn vào vi điều khiển.

- Ghi dữ liệu vào chip nhớ.

Code Verilog cho Thanh Ghi PISO

module Shiftregister_PISO(Clk, Parallel_In,load, Serial_Out);

input Clk,load;

input [3:0]Parallel_In;

output reg Serial_Out;

reg [3:0]tmp;

always @(posedge Clk) begin

if(load)

tmp <= Parallel_In;

else begin

Serial_Out <= tmp[0];

tmp <= tmp >> 1;

end

end

endmoduleKết Luận

Thanh ghi dịch chuyển vào song song ra nối tiếp (PISO) là một thành phần quan trọng trong thiết kế hệ thống kỹ thuật số. Hiểu rõ về bảng chân lý thanh ghi dịch chuyển vào song song ra nối tiếp (parallel in serial out shift register truth table), nguyên lý hoạt động và ứng dụng của nó sẽ giúp kỹ sư thiết kế các hệ thống hiệu quả và đáng tin cậy. Việc sử dụng code Verilog giúp mô phỏng và kiểm tra hoạt động của thanh ghi PISO trước khi triển khai trên phần cứng.