Thanh ghi dịch chuyển là một tập hợp các flip-flop được sử dụng để lưu trữ nhiều bit dữ liệu bằng cách kết nối chúng nối tiếp. Dữ liệu được lưu trữ trong các thanh ghi này có thể được dịch chuyển bằng cách sử dụng tín hiệu xung nhịp (CLK). Bài viết này sẽ tập trung vào loại thanh ghi dịch chuyển PISO (Parallel In Serial Out), hay còn gọi là thanh ghi dịch chuyển nhập song song xuất nối tiếp, và code Verilog của nó.

Thanh ghi PISO hoạt động bằng cách nhận dữ liệu đầu vào song song và xuất ra dữ liệu nối tiếp. Điều này ngược lại với hoạt động của thanh ghi SIPO (Serial In Parallel Out). Trong thanh ghi PISO, dữ liệu đầu vào được đưa vào đồng thời tại tất cả các chân vào, sau đó được đọc ra từng bit một tại chân xuất theo mỗi chu kỳ xung nhịp.

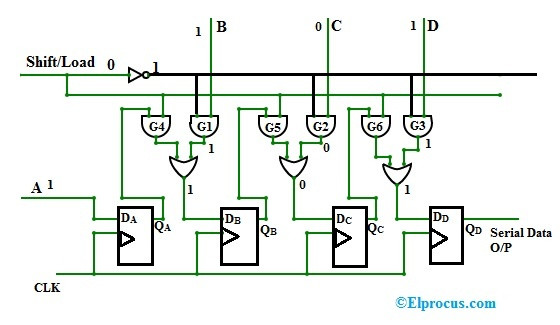

Một mạch thanh ghi PISO điển hình bao gồm một số flip-flop D được kết nối theo kiểu nối tiếp. Tín hiệu CLK được kết nối với tất cả các flip-flop, trong khi dữ liệu đầu vào được kết nối riêng biệt với mỗi flip-flop. Đầu ra của mỗi flip-flop được kết nối với đầu vào của flip-flop tiếp theo.

Mô tả hoạt động:

Giả sử dữ liệu đầu vào là 1101. Khi tín hiệu điều khiển (Shift/Load) ở mức thấp (0), dữ liệu được nạp song song vào các flip-flop. Khi tín hiệu điều khiển ở mức cao (1) và có xung CLK, dữ liệu sẽ được dịch chuyển sang phải từng bit một. Sau mỗi xung CLK, bit ở vị trí cuối cùng (QD) sẽ là dữ liệu đầu ra nối tiếp. Quá trình này tiếp tục cho đến khi tất cả các bit dữ liệu được dịch chuyển ra.

Bảng chân lý:

Bảng dưới đây minh họa quá trình dịch chuyển dữ liệu trong thanh ghi PISO với dữ liệu đầu vào là 1101.

| CLK Pulse | QA | QB | Qc | QD (Data Output) |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 2 | 0 | 1 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 0 | 0 | 1 |

Code Verilog cho thanh ghi PISO:

Dưới đây là một ví dụ về code Verilog cho thanh ghi PISO 4 bit:

module Shiftregister_PISO(Clk, Parallel_In,load, Serial_Out);

input Clk,load;

input [3:0] Parallel_In;

output reg Serial_Out;

reg [3:0] tmp;

always @(posedge Clk) begin

if(load)

tmp <= Parallel_In;

else begin

Serial_Out <= tmp[3];

tmp <= tmp << 1;

end

end

endmoduleỨng dụng:

Thanh ghi PISO được sử dụng rộng rãi trong nhiều ứng dụng, bao gồm:

- Chuyển đổi dữ liệu từ dạng song song sang dạng nối tiếp.

- Tạo độ trễ thời gian trong mạch kỹ thuật số.

- Đọc dữ liệu từ nhiều công tắc vào một chip chỉ sử dụng một vài chân.

- Đọc dữ liệu vào chip nhớ.

Code Verilog trên mô tả một thanh ghi dịch chuyển PISO 4 bit. Tín hiệu load được sử dụng để điều khiển việc nạp dữ liệu vào thanh ghi. Khi load ở mức cao, dữ liệu từ Parallel_In được nạp vào thanh ghi. Khi load ở mức thấp, dữ liệu trong thanh ghi được dịch chuyển sang trái một bit tại mỗi cạnh lên của tín hiệu clock Clk, và bit ngoài cùng bên phải được xuất ra tại Serial_Out.