Vi điều khiển 8051 sở hữu một tập hợp các thanh ghi chức năng đặc biệt (Special Function Registers – SFRs) điều khiển các chức năng và thiết bị ngoại vi khác nhau. Các thanh ghi này rất cần thiết để lập trình hoạt động của vi điều khiển.

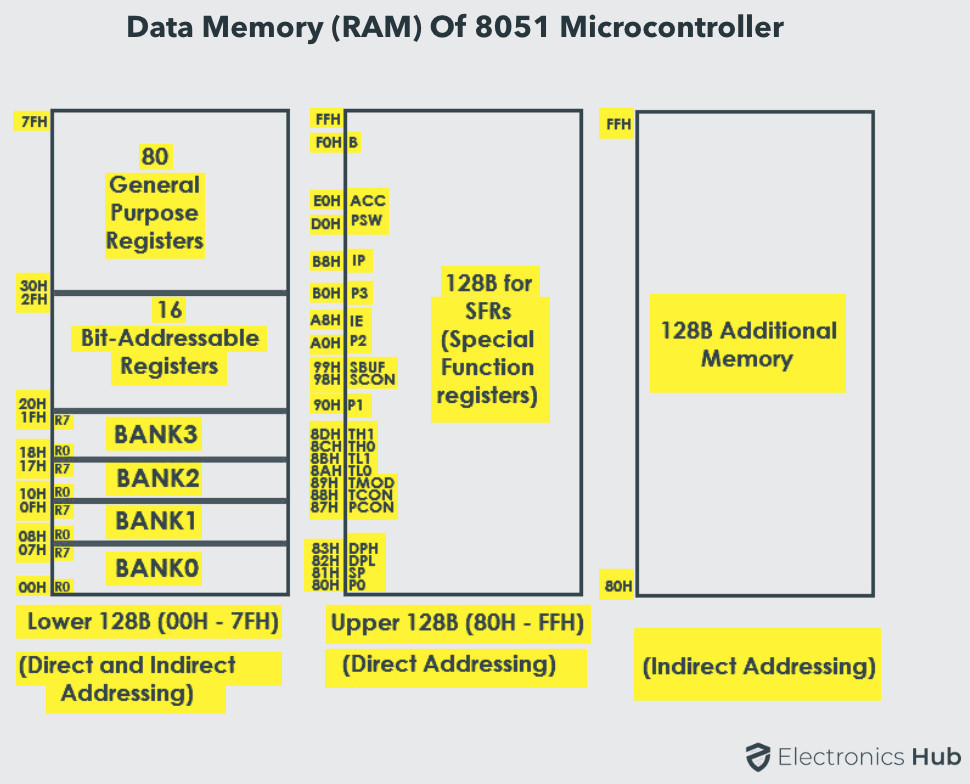

RAM bên trong hoặc bộ nhớ dữ liệu của vi điều khiển 8051 được chia thành các thanh ghi đa năng, thanh ghi địa chỉ bit, ngân hàng thanh ghi và thanh ghi chức năng đặc biệt.

Thanh ghi chức năng đặc biệt trong 8051 là gì?

Thanh ghi chức năng đặc biệt trong vi điều khiển 8051 được sử dụng để lập trình và điều khiển các thiết bị ngoại vi phần cứng khác nhau như Timer, cổng nối tiếp, cổng I/O, v.v. Bằng cách thao tác với SFR trong vi điều khiển 8051, bạn có thể đánh giá hoặc thay đổi chế độ hoạt động của vi điều khiển 8051.

Hình ảnh sau đây cho thấy cấu trúc cơ bản của RAM bên trong của vi điều khiển 8051.

Thanh ghi chức năng đặc biệt (SFRs) của vi điều khiển 8051

SFR trong vi điều khiển 8051 hoạt động như một bảng điều khiển giám sát và điều khiển hoạt động của vi điều khiển 8051. Không gian địa chỉ từ 80H đến FFH trong cấu trúc RAM bên trong được phân bổ cho SFRs.

Trong số 128 vị trí bộ nhớ này (80H đến FFH), chỉ có 21 vị trí thực sự được gán cho SFRs. Mỗi SFR có một địa chỉ byte và một tên duy nhất xác định mục đích của nó.

Vì SFRs là một phần của cấu trúc RAM bên trong, bạn có thể truy cập SFRs như khi bạn truy cập RAM bên trong. Sự khác biệt chính là không gian địa chỉ: 128 byte đầu tiên (00H đến 7FH) dành cho RAM bên trong thông thường và 128 byte tiếp theo (80H đến FFH) dành cho SFRs.

Lưu ý: Vì chỉ có 21 trong số 128 vị trí bộ nhớ SFR có thể có được gán, nên khuyến nghị không truy cập các thanh ghi hoặc vị trí bộ nhớ còn lại trong quá trình lập trình.

Danh sách các thanh ghi chức năng đặc biệt trong vi điều khiển 8051

- Thanh ghi tích lũy (A)

- Thanh ghi B (B)

- Từ trạng thái chương trình (PSW)

- Con trỏ dữ liệu (DPTR)

- Con trỏ ngăn xếp (SP)

- DPL (Byte thấp của con trỏ dữ liệu)

- DPH (Byte cao của con trỏ dữ liệu)

- Thanh ghi cho phép ngắt (IE)

- Thanh ghi ưu tiên ngắt (IP)

- Thanh ghi cổng I/O (P0, P1, P2, P3)

- Thanh ghi điều khiển nguồn (PCON)

- Thanh ghi điều khiển nối tiếp (SCON)

- SBUF (Thanh ghi đệm nối tiếp)

- Thanh ghi Timer/Counter (TMOD, TH0, TL0, TH1, TL1)

Phân loại thanh ghi chức năng đặc biệt của vi điều khiển 8051

Bảng sau đây liệt kê tất cả 21 thanh ghi chức năng đặc biệt của vi điều khiển 8051 cùng với chức năng và địa chỉ RAM bên trong của chúng.

Có nhiều cách để phân loại 21 thanh ghi chức năng đặc biệt này nhưng cách sau đây được coi là phù hợp. 21 thanh ghi chức năng đặc biệt của vi điều khiển 8051 được phân loại thành bảy nhóm.

Các loại thanh ghi chức năng đặc biệt (SFRs) khác nhau trong vi điều khiển 8051:

- Thanh ghi toán học hoặc CPU: A và B

- Thanh ghi trạng thái: PSW (Program Status Word)

- Thanh ghi con trỏ: DPTR (Data Pointer – DPL, DPH) và SP (Stack Pointer)

- Chốt cổng I/O: P0 (Port 0), P1 (Port 1), P2 (Port 2) và P3 (Port 3)

- Thanh ghi điều khiển ngoại vi: PCON, SCON, TCON, TMOD, IE và IP

- Thanh ghi dữ liệu ngoại vi: TL0, TH0, TL1, TH1 và SBUF

Thanh ghi CPU hoặc toán học của vi điều khiển 8051:

A hoặc Thanh ghi tích lũy (ACC)

Thanh ghi tích lũy hoặc Thanh ghi A là SFR quan trọng nhất và được sử dụng nhiều nhất trong vi điều khiển 8051. Thanh ghi A nằm tại địa chỉ E0H trong không gian bộ nhớ SFR. Thanh ghi tích lũy được sử dụng để lưu trữ dữ liệu cho hầu hết tất cả các hoạt động ALU.

Một số hoạt động mà Thanh ghi tích lũy được sử dụng là:

- Các phép toán số học như cộng, trừ, nhân, v.v.

- Các phép toán logic như AND, OR, NOT, v.v.

- Các phép toán truyền dữ liệu (giữa 8051 và bộ nhớ ngoài)

Tên “Thanh ghi tích lũy” xuất phát từ việc thanh ghi này được sử dụng để tích lũy (hoặc lưu trữ) kết quả của tất cả các phép toán số học và hầu hết các phép toán logic.

B (Thanh ghi B)

Thanh ghi B được sử dụng cùng với ACC trong các phép toán nhân và chia. Hai phép toán này được thực hiện trên dữ liệu chỉ được lưu trữ trong Thanh ghi A và B. Trong phép toán nhân, một trong các toán hạng (số nhân hoặc số bị nhân) được lưu trữ trong Thanh ghi B và cả byte cao hơn của kết quả.

Trong trường hợp phép toán chia, Thanh ghi B chứa số chia và phần dư của kết quả. Nó cũng có thể được sử dụng như một thanh ghi đa năng cho các hoạt động thông thường và thường được các lập trình viên sử dụng làm thanh ghi phụ để lưu trữ kết quả tạm thời.

Thanh ghi B nằm tại địa chỉ F0H của không gian địa chỉ SFR.

Từ trạng thái chương trình (PSW)

Thanh ghi PSW hoặc Program Status Word còn được gọi là Thanh ghi cờ và là một trong những SFR quan trọng. Thanh ghi PSW bao gồm các bit cờ, giúp lập trình viên kiểm tra điều kiện của kết quả và đưa ra quyết định.

Cờ là các phần tử lưu trữ 1 bit lưu trữ và chỉ ra bản chất của kết quả được tạo ra bằng cách thực hiện một số lệnh nhất định. Hình ảnh sau đây hiển thị nội dung của Thanh ghi PSW.

Bảng sau đây mô tả chức năng của từng cờ.

Thanh ghi con trỏ

Con trỏ dữ liệu (DPTR – DPL và DPH)

Con trỏ dữ liệu là một thanh ghi 16 bit và về mặt vật lý là sự kết hợp của các SFR DPL (Data Pointer Low) và DPH (Data Pointer High). Con trỏ dữ liệu có thể được sử dụng như một thanh ghi 16 bit duy nhất (như DPTR) hoặc hai thanh ghi 8 bit (như DPL và DPH).

DPTR không có địa chỉ bộ nhớ vật lý nhưng DPL (Byte thấp hơn của DPTR) và DPH (Byte cao hơn của DPTR) có địa chỉ riêng biệt trong không gian bộ nhớ SFR. DPL = 82H và DPH = 83H.

Thanh ghi DPTR được lập trình viên sử dụng để định địa chỉ bộ nhớ ngoài (Chương trình – ROM hoặc Dữ liệu – RAM).

Con trỏ ngăn xếp (SP)

SP hoặc Con trỏ ngăn xếp trỏ đến đầu ngăn xếp và nó chỉ ra dữ liệu tiếp theo sẽ được truy cập. Có thể truy cập Con trỏ ngăn xếp bằng các lệnh PUSH, POP, CALL và RET. Con trỏ ngăn xếp là một thanh ghi 8 bit và khi đặt lại, Con trỏ ngăn xếp được khởi tạo với giá trị 07H.

Khi ghi một byte dữ liệu mới vào ngăn xếp, SP (Con trỏ ngăn xếp) sẽ tự động tăng thêm 1 và dữ liệu mới được ghi vào địa chỉ SP+1. Khi đọc dữ liệu từ ngăn xếp, dữ liệu được lấy từ Địa chỉ trong SP và sau đó SP giảm đi 1 (SP-1).

Thanh ghi cổng I/O (P0, P1, P2 và P3)

Vi điều khiển 8051 có bốn cổng có thể được sử dụng làm đầu vào và / hoặc đầu ra. Bốn cổng này là P0, P1, P2 và P3. Mỗi cổng có một thanh ghi tương ứng có cùng tên (các thanh ghi cổng cũng là P0, P1, P2 và P3). Địa chỉ của Thanh ghi cổng như sau: P0 – 80H, P1 – 90H, P2 – A0H và P3 – B0H.

Mỗi bit trong các SFR này tương ứng với một chân vật lý trong vi điều khiển 8051. Tất cả các Thanh ghi cổng này đều có thể định địa chỉ bit và byte. Việc ghi 1 hoặc 0 trên một bit Thanh ghi cổng sẽ phản ánh điện áp thích hợp (5V và 0V) trên chân tương ứng.

Nếu một bit cổng được SET (khai báo là 1), chân cổng tương ứng sẽ được cấu hình là Đầu vào và tương tự nếu một bit cổng được CLEARED (khai báo là 0), chân cổng tương ứng được cấu hình là Đầu ra. Khi đặt lại, tất cả các bit cổng đều được SET (1) và do đó, tất cả các chân cổng đều được cấu hình là Đầu vào.

Vẽ và giải thích cấu trúc cổng với SFR được sử dụng trong lập trình

Thanh ghi điều khiển ngoại vi

PCON (Điều khiển nguồn)

Thanh ghi PCON hoặc Điều khiển nguồn, đúng như tên gọi của nó, được sử dụng để điều khiển Chế độ nguồn của vi điều khiển 8051 và nằm tại 87H của không gian bộ nhớ SFR. Sử dụng hai bit trong Thanh ghi PCON, vi điều khiển có thể được đặt ở Chế độ nhàn rỗi và Chế độ tắt nguồn.

LƯU Ý: Thanh ghi PCON không thể định địa chỉ bit.

Ở chế độ nhàn rỗi, vi điều khiển sẽ dừng tín hiệu xung nhịp tới ALU (CPU) nhưng nó được cấp cho các thiết bị ngoại vi khác như Timer, nối tiếp, ngắt, v.v. Để kết thúc chế độ nhàn rỗi, bạn phải sử dụng Ngắt hoặc đặt lại phần cứng.