Thanh ghi nói chung là một thiết bị dùng để lưu trữ dữ liệu nhị phân. Tuy nhiên, nếu muốn lưu trữ nhiều bit dữ liệu, cần sử dụng một tập hợp các Flip-flop được kết nối nối tiếp. Dữ liệu được lưu trữ trong thanh ghi có thể được dịch chuyển bằng cách sử dụng thanh ghi dịch chuyển sang bên phải hoặc bên trái bằng cách cung cấp xung CLK. Thanh ghi dịch chuyển là một nhóm các flip-flop được sử dụng để lưu trữ nhiều bit dữ liệu. Tương tự, một thanh ghi dịch chuyển n-bit có thể được hình thành bằng cách kết nối n flip-flop, mỗi flip-flop lưu trữ một bit dữ liệu duy nhất. Nếu thanh ghi dịch chuyển bit sang bên phải, nó là thanh ghi dịch phải; nếu nó dịch chuyển sang bên trái, nó được gọi là thanh ghi dịch trái. Bài viết này thảo luận tổng quan về một loại thanh ghi dịch chuyển, đó là thanh ghi dịch chuyển nối tiếp vào song song ra hay SIPO shift register.

Thanh ghi dịch chuyển cho phép nhập nối tiếp và xuất song song được gọi là thanh ghi dịch chuyển SIPO. Trong thanh ghi SIPO, thuật ngữ SIPO là viết tắt của Serial Input Parallel Output (nhập nối tiếp xuất song song). Trong loại thanh ghi dịch chuyển này, dữ liệu đầu vào được đưa vào từng bit một cách nối tiếp. Đối với mỗi xung clock, dữ liệu đầu vào tại tất cả các FF có thể được dịch chuyển một vị trí. Đầu ra tại mỗi flip-flop có thể được nhận song song.

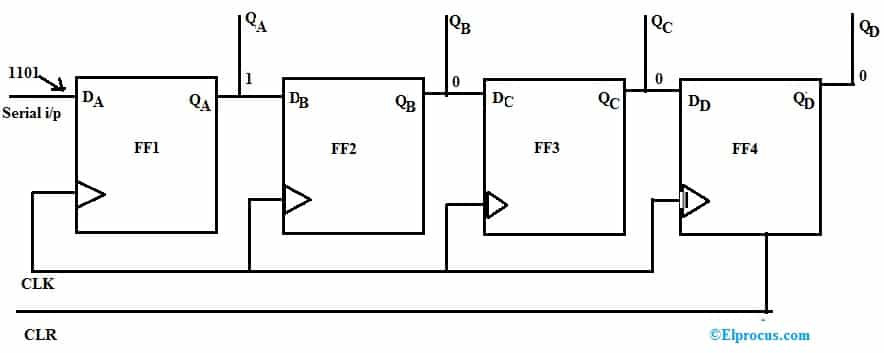

Sơ đồ mạch của SIPO shift register được hiển thị bên dưới. Mạch này có thể được xây dựng với 4 flip-flop D được kết nối như trong sơ đồ, trong đó tín hiệu CLR được cấp bổ sung cho tín hiệu CLK cho tất cả các FF để RESET chúng. Trong mạch trên, đầu ra FF đầu tiên được đưa vào đầu vào FF thứ hai. Cả bốn flip-flop D này được kết nối với nhau nối tiếp vì cùng một tín hiệu CLK được đưa vào mỗi flip-flop.

Nguyên lý hoạt động của thanh ghi dịch chuyển SIPO là nhận dữ liệu đầu vào nối tiếp từ flip-flop đầu tiên ở bên trái và tạo ra đầu ra dữ liệu song song. Mạch thanh ghi dịch chuyển SIPO 4 bit được hiển thị ở trên. Hoạt động của thanh ghi dịch chuyển này là đầu tiên tất cả các flip-flop từ FF1 đến FF4 phải được RESET để tất cả các đầu ra của FF như QA đến QD sẽ ở mức logic 0, do đó không có đầu ra dữ liệu song song.

Trong sơ đồ, đầu ra flip-flop đầu tiên ‘QA’ được kết nối với đầu vào flip-flop thứ hai ‘DB’. Đầu ra flip-flop thứ hai ‘QB’ được kết nối với đầu vào flip-flop thứ ba ‘DC’, và đầu ra flip-flop thứ ba ‘QC’ được kết nối với đầu vào flip-flop thứ tư ‘DD’. Ở đây, QA, QB, QC và QD là các đầu ra dữ liệu.

Ban đầu, tất cả đầu ra sẽ bằng không nên nếu không có xung CLK, tất cả dữ liệu sẽ bằng không. Lấy ví dụ đầu vào dữ liệu 4 bit là 1101. Nếu áp dụng xung clock đầu tiên ‘1’ cho flip-flop đầu tiên, dữ liệu được nhập vào FF và QA trở thành ‘1’, và tất cả các đầu ra còn lại như QB, QC và QD sẽ trở thành không. Vì vậy, đầu ra dữ liệu đầu tiên là ‘1000’.

Nếu áp dụng xung clock thứ hai là ‘0’ cho flip-flop đầu tiên thì QA trở thành ‘0’, QB trở thành ‘1’, QC trở thành ‘0’ và QD trở thành ‘0’. Vì vậy, đầu ra dữ liệu thứ hai sẽ trở thành ‘0100’ do quá trình dịch phải.

Nếu áp dụng xung clock thứ ba là ‘1’ cho flip-flop đầu tiên thì QA trở thành ‘1’, QB trở thành ‘0’, QC trở thành ‘1’ và QD trở thành ‘0’. Vì vậy, đầu ra dữ liệu thứ ba sẽ trở thành ‘1010’ do quá trình dịch phải. Nếu áp dụng xung clock thứ tư là ‘1’ cho flip-flop đầu tiên thì QA trở thành ‘1’, QB trở thành ‘1’, QC trở thành ‘0’ và QD trở thành ‘1’. Vì vậy, đầu ra dữ liệu thứ tư sẽ trở thành ‘1101’ do quá trình dịch phải.

Bảng chân lý của thanh ghi dịch chuyển SIPO được hiển thị bên dưới.

Sơ đồ thời gian của thanh ghi dịch chuyển SIPO được hiển thị bên dưới.

Ở đây, chúng ta đang sử dụng tín hiệu CLK cạnh dương. Trong xung clock đầu tiên, dữ liệu đầu vào trở thành QA = ‘1’ và tất cả các giá trị khác như QB, QC và QD trở thành ‘0’. Vì vậy, đầu ra sẽ là ‘1000’. Trong xung clock thứ hai, đầu ra sẽ là ‘0100’. Trong xung clock thứ ba, đầu ra sẽ là ‘0010’ và trong xung clock thứ tư, đầu ra sẽ là ‘0001’.

Mã Verilog cho thanh ghi dịch chuyển SIPO được hiển thị bên dưới.

module sipomod(clk,clear, si, po);

input clk, si,clear;

output [3:0] po;

reg [3:0] tmp;

reg [3:0] po;

always @(posedge clk) begin

if (clear)

tmp <= 4'b0000;

else

tmp <= {tmp[2:0], si};

po <= tmp;

end

endmodule

IC 74HC595 là một thanh ghi dịch chuyển nối tiếp vào song song ra 8 bit, vì vậy nó sử dụng đầu vào nối tiếp và cung cấp đầu ra song song. IC này bao gồm 16 chân và có sẵn trong các gói khác nhau như SOIC, DIP, TSSOP & SSOP.

Ứng dụng của thanh ghi dịch chuyển nối tiếp vào song song ra được thể hiện như sau:

- Thanh ghi dịch chuyển thường được sử dụng để lưu trữ dữ liệu tạm thời, được sử dụng như bộ đếm vòng và Johnson.

- Chúng được sử dụng để truyền và xử lý dữ liệu.

- Các flip-flop này chủ yếu được sử dụng trong các đường truyền thông, nơi cần giải mã một đường dữ liệu thành nhiều đường song song, vì thanh ghi dịch chuyển này được sử dụng để thay đổi dữ liệu từ nối tiếp sang song song.

- Chúng được sử dụng để mã hóa và giải mã dữ liệu.

- Thanh ghi dịch chuyển này được sử dụng trong CDMA để tạo mã PN hoặc Số dãy nhiễu giả.

- Thanh ghi dịch chuyển SIPO được sử dụng trong các ứng dụng kỹ thuật số khác nhau để chuyển đổi dữ liệu.

- Đôi khi, loại thanh ghi dịch chuyển này chỉ cần kết nối với vi xử lý khi cần thêm chân GPIO.

- Ứng dụng thực tế của thanh ghi dịch chuyển SIPO này là cung cấp dữ liệu đầu ra của vi xử lý cho đèn báo hiệu bảng điều khiển từ xa.