Thanh ghi dịch chuyển SISO (Serial In, Serial Out) là một mạch điện tử kỹ thuật số quan trọng được sử dụng rộng rãi trong việc xử lý và lưu trữ dữ liệu tuần tự. Bài viết này sẽ đi sâu vào tìm hiểu nguyên lý hoạt động, sơ đồ mạch, code Verilog và ứng dụng của thanh ghi dịch chuyển SISO.

Thanh ghi Dịch chuyển SISO là gì?

SISO là viết tắt của “Serial-In, Serial-Out”, nghĩa là dữ liệu được nhập vào và xuất ra theo kiểu tuần tự, bit theo bit. Thanh ghi SISO nhận dữ liệu tuần tự tại chân đầu vào và dịch chuyển nó ra theo thứ tự tại chân đầu ra. Số lượng bit có thể được dịch chuyển ra trước khi bit tiếp theo đến phụ thuộc vào tốc độ xung nhịp điều khiển hoạt động của thanh ghi. Loại thanh ghi này thường được sử dụng như một bộ đệm giữa hai thiết bị không đồng bộ giao tiếp với nhau bằng các tín hiệu có tần số hoặc pha khác nhau.

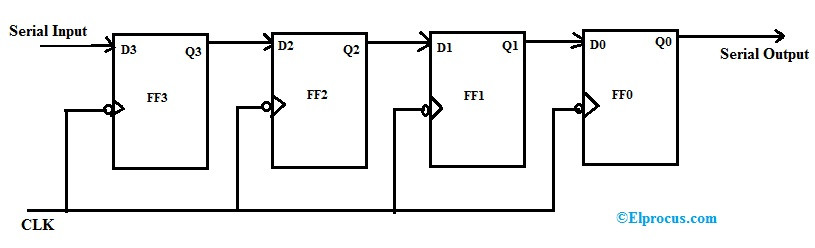

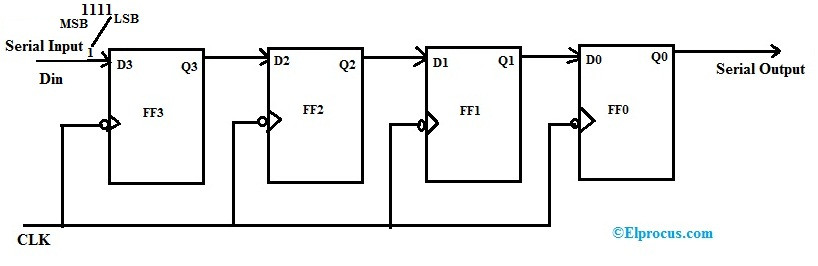

Sơ đồ khối trên minh họa một thanh ghi SISO sử dụng 3 flip-flop kiểu D. Các flip-flop này được kết nối nối tiếp với nhau, đầu ra của flip-flop trước là đầu vào của flip-flop tiếp theo. Chúng hoạt động đồng bộ nhờ tín hiệu xung nhịp CLK chung. Ba kết nối quan trọng trong thanh ghi SISO là: SI (Serial Input – đầu vào tuần tự), SO (Serial Output – đầu ra tuần tự) và CLK (Clock – xung nhịp).

Nguyên Lý Hoạt Động

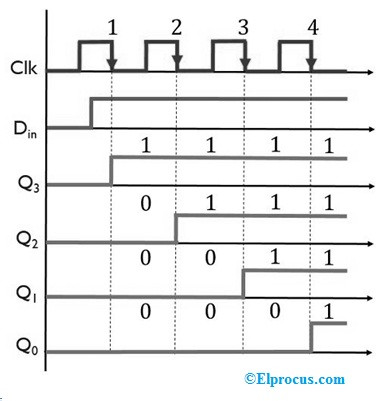

Dữ liệu được đưa vào bit đầu tiên tại chân SI của flip-flop ngoài cùng bên trái. Với mỗi xung nhịp CLK, dữ liệu được dịch chuyển sang phải một vị trí. Bit ở vị trí ngoài cùng bên phải sẽ được xuất ra tại chân SO. Ví dụ, với dữ liệu đầu vào là 1011, quá trình dịch chuyển sẽ diễn ra như sau:

| CLK | Q3 | Q2 | Q1 | Q0 (SO) |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 1 | 0 | 1 | 0 |

| 4 | 1 | 1 | 0 | 1 |

Biểu diễn dạng sóng trên cho thấy tín hiệu CLK, dữ liệu đầu vào và đầu ra của từng flip-flop. Mỗi khi có xung xuống của CLK, dữ liệu được dịch chuyển sang phải.

Sơ Đồ Mạch

Sơ đồ mạch sử dụng 4 flip-flop loại D được kết nối nối tiếp. Dữ liệu được nhập vào tại D3 và xuất ra tại Q0.

siso shift register verilog code

module sisomod(clk,clear,si,so);

input clk,si,clear;

output so;

reg so;

reg [3:0] tmp;

always @(posedge clk) begin

if (clear)

tmp <= 4'b0000;

else

tmp <= {tmp[2:0], si};

end

assign so = tmp[3];

endmoduleĐoạn code Verilog trên mô tả một thanh ghi SISO 4 bit. Tín hiệu clk là xung nhịp, clear là tín hiệu reset, si là đầu vào tuần tự và so là đầu ra tuần tự.

Ứng Dụng

Thanh ghi dịch chuyển SISO có nhiều ứng dụng trong các hệ thống kỹ thuật số, bao gồm:

- Tạo độ trễ thời gian trong mạch logic.

- Truyền, xử lý và lưu trữ dữ liệu tuần tự.

- Giảm số lượng dây kết nối giữa các hệ thống trong thiết kế.

- Ứng dụng trong truyền thông nối tiếp.

Kết luận

Thanh ghi dịch chuyển SISO là một thành phần cơ bản trong thiết kế hệ thống kỹ thuật số. Hiểu rõ nguyên lý hoạt động và cách viết code Verilog cho thanh ghi SISO là rất quan trọng đối với các kỹ sư thiết kế phần cứng. Siso Shift Register Verilog Code cung cấp một giải pháp hiệu quả cho việc xử lý dữ liệu tuần tự trong nhiều ứng dụng khác nhau.